Good day!

I am attaching the code of full adder and simulation results. Please do have a look and let me know my mistakes.

.param psu = 0.9V

.param len = 16n

.param wpmos=100n wnmos=50n

vsupply vdd 0 {psu}

vgnd vss 0 0V

*Inputs to transistors

vina va vss PULSE(0 {psu} 2NS 2NS 2NS 60NS 120NS)

vinb vb vss PULSE(0 {psu} 2NS 2NS 2NS 80NS 160NS)

vinc vc vss PULSE(0 {psu} 2NS 2NS 2NS 90NS 200NS)

*Function for sum

Mpb vbbar vb vdd vdd pmos l={len} w={wpmos} ; pmos

Mnb vbbar vb vss vss nmos l={len} w={wnmos} ; nmos

Mpa vabar va vdd vdd pmos l={len} w={wpmos} ; pmos

Mna vabar va vss vss nmos l={len} w={wnmos} ; nmos

Mpc vcbar vc vdd vdd pmos l={len} w={wpmos} ; pmos

Mnc vcbar vc vss vss nmos l={len} w={wnmos} ; nmos

******************MOSFETs drain gate source body

*sum inputs(a b c)

Mp1 vdr1 va vdd vdd pmos l={len} w={wpmos} ; pmos

Mp2 vdr2 vabar vdd vdd pmos l={len} w={wpmos} ; pmos

Mp3 vdr3 va vdd vdd pmos l={len} w={wpmos} ; pmos

Mp4 vdr4 vabar vdd vdd pmos l={len} w={wpmos} ; pmos

Mp5 vdr5 vbbar vdr1 vdd pmos l={len} w={wpmos} ; pmos

Mp6 vdr6 vb vdr2 vdd pmos l={len} w={wpmos} ; pmos

Mp7 vdr7 vb vdr3 vdd pmos l={len} w={wpmos} ; pmos

Mp8 vdr8 vbbar vdr4 vdd pmos l={len} w={wpmos} ; pmos

Mp9 vout vc vdr5 vdd pmos l={len} w={wpmos} ; pmos

Mp10 vout vc vdr6 vdd pmos l={len} w={wpmos} ; pmos

Mp11 vout vcbar vdr7 vdd pmos l={len} w={wpmos} ; pmos

Mp12 vout vcbar vdr8 vdd pmos l={len} w={wpmos} ; pmos

Mn1 vout va vdr9 vss nmos l={len} w={wnmos} ; nmos

Mn2 vout vbbar vdr9 vss nmos l={len} w={wnmos} ; nmos

Mn3 vout vc vdr9 vss nmos l={len} w={wnmos} ; nmos

Mn4 vdr9 vabar vdr10 vss nmos l={len} w={wnmos} ; nmos

Mn5 vdr9 vb vdr10 vss nmos l={len} w={wnmos} ; nmos

Mn6 vdr9 vc vdr10 vss nmos l={len} w={wnmos} ; nmos

Mn7 vdr10 va vdr11 vss nmos l={len} w={wnmos} ; nmos

Mn8 vdr10 vb vdr11 vss nmos l={len} w={wnmos} ; nmos

Mn9 vdr10 vcbar vdr11 vss nmos l={len} w={wnmos} ; nmos

Mn10 vdr11 vabar vss vss nmos l={len} w={wnmos} ; nmos

Mn11 vdr11 vbbar vss vss nmos l={len} w={wnmos} ; nmos

Mn12 vdr11 vcbar vss vss nmos l={len} w={wnmos} ; nmos

*carry inputs(a b c)

Mp11a vdr1c vabar vdd vdd pmos l={len} w={wpmos} ; pmos

Mp21 vdr2c vbbar vdd vdd pmos l={len} w={wpmos} ; pmos

Mp31 vdr3c vcbar vdd vdd pmos l={len} w={wpmos} ; pmos

Mp41 voutc vbbar vdr1c vdd pmos l={len} w={wpmos} ; pmos

Mp51 voutc vcbar vdr2c vdd pmos l={len} w={wpmos} ; pmos

Mp61 voutc vabar vdr3c vdd pmos l={len} w={wpmos} ; pmos

Mn11a voutc vabar vdr4c vss nmos l={len} w={wnmos} ; nmos

Mn21 voutc vbbar vdr4c vss nmos l={len} w={wnmos} ; nmos

Mn31 vdr4c vbbar vdr5c vss nmos l={len} w={wnmos} ; nmos

Mn41 vdr4c vcbar vdr5c vss nmos l={len} w={wnmos} ; nmos

Mn51 vdr5c vcbar vss vss nmos l={len} w={wnmos} ; nmos

Mn61 vdr5c vabar vss vss nmos l={len} w={wnmos} ; nmos

Cload1 vout vss1 200f

vdc1 vss1 vss dc 0V

Cload2 voutc vss2 200f

vdc2 vss2 vss dc 0V

.options method=gear reltol=0.1m

.tran 0.1n 200n 0 0.1n

.save all @vsupply[p]

.control

run

*delay for sum

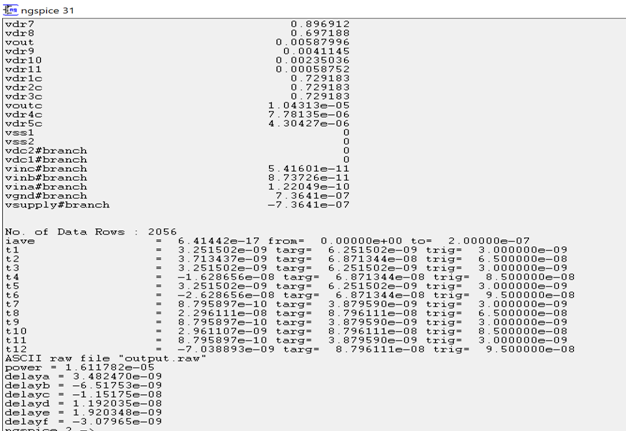

meas tran t1 TRIG va VAL=0.45 rise=1 TARG vout VAL=0.45 rise=1

meas tran t2 TRIG va VAL=0.45 fall=1 TARG vout VAL=0.45 fall=1

meas tran t3 TRIG vb VAL=0.45 rise=1 TARG vout VAL=0.45 rise=1

meas tran t4 TRIG vb VAL=0.45 fall=1 TARG vout VAL=0.45 fall=1

meas tran t5 TRIG vc VAL=0.45 rise=1 TARG vout VAL=0.45 rise=1

meas tran t6 TRIG vc VAL=0.45 fall=1 TARG vout VAL=0.45 fall=1

let delaya = (t1+t2)/2

let delayb = (t3+t4)/2

let delayc = (t5+t6)/2

*delay for carry

meas tran t7 TRIG va VAL=0.45 rise=1 TARG voutc VAL=0.45 rise=1

meas tran t8 TRIG va VAL=0.45 fall=1 TARG voutc VAL=0.45 fall=1

meas tran t9 TRIG vb VAL=0.45 rise=1 TARG voutc VAL=0.45 rise=1

meas tran t10 TRIG vb VAL=0.45 fall=1 TARG voutc VAL=0.45 fall=1

meas tran t11 TRIG vc VAL=0.45 rise=1 TARG voutc VAL=0.45 rise=1

meas tran t12 TRIG vc VAL=0.45 fall=1 TARG voutc VAL=0.45 fall=1

let delayd = (t7+t8)/2

let delaye = (t9+t10)/2

let delayf = (t11+t12)/2

set filetype = ascii

write output.raw v(va) v(vout)

plot v(va) v(vb) v(vc)

plot v(vout) v(voutc)

print delaya delayb delayc delayd delaye delayf

.endc

.End

Finally

Delay for sum= delaya+delayb+delayc/3

Delay for carry= delayd+delaye+delayf/3

Delay for sum= 7.1666ns

Delay for carry= 5.6366ns